# 10W Stereo Class D Audio Power Amplifier

**BA3101**

# **Data Sheet**

Rev.1.0, 2009.08.01

Biforst Technology Inc.

# 10W Stereo Class D Audio Power Amplifier

## **GENERAL DESCRIPTION**

BA3101

The BA3101 is a 12V class D amplifier from Biforst Technology. BA3101 provide volume control with four selectable gain settings. BA3101 is a 10-W (per channel) with lower supply current and fewer external components for driving bridged-tied stereo speaker directly.

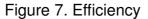

BA3101 operates with high efficiency energy conversion up to 89% (8-Ω Load) so that the external heat sink can be eliminated while playing music. Two gain select pins, GAIN0 and GAIN1, control the two controllable gain values, with firm gain selections are 20dB, 26dB, 32dB, 36dB.

BA3101 also integrates Anti-Pop, Output Short & Over-Heat Protection Circuitry to ensure device reliability. This device output are completely protected from shorts to ground or supply pin as well as protected from Output Pin to Output Pin short. All the output short protection features are auto restore and auto monitor.

## FEATURE

- 9.2W Per Channel Into 8- $\Omega$  Speakers (THD+N = 10%@12V)

- 10.8W Per Channel into 8-Ω Speakers (THD+N = 10%@13V)

- Operation Voltage From 8V To 15V

- Maximum Power Efficiency Into 8-Ω, 89%

- Total four selectable, firm-gain solution

- Differential input

- Automatic monitor and restore scheme for short and over heat protection

- Clock synchronization master/slave for multiple Class D device

- Eliminates output clamp and bypass capacitors

- Package is SMD 7mm \* 7mm 48 Pins TQFP-with Exposed Thermal Pad

## **APPLICATION**

- LCD TV

- LCD Monitor

- Powered Speaker

- Hi-Fi Audio System

These devices have limited built-in ESD protection. The lead should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the device.

#### **ABSOLUTE MAXIMUM RATINGS**

BA3101

Over operating free-air temperature range, unless otherwise specified (\* 1)

| SYMBOL                              | PARAMETER                                             | VALUE            | UNIT |

|-------------------------------------|-------------------------------------------------------|------------------|------|

| VDD, PVDDL, PVDDR                   | Supply voltage                                        | -0.3 to 15       | V    |

| V <sub>I</sub> (SHUTDOWN, MUTE)     | Input voltage                                         | -0.3 to VCC+0.3  | V    |

| V <sub>I</sub> (GAIN0, GAIN1, RINN, |                                                       |                  |      |

| RINP, LINN, LINP, MSTR/ SLV ,       | Input voltage                                         | -0.3 to VREG+0.5 | V    |

| SYNC)                               |                                                       |                  |      |

| T <sub>A</sub>                      | Operating free-air temperature range                  | -40 ~ +85        | °C   |

| TJ                                  | Operating junction temperature range <sup>(* 2)</sup> | -40 to +150      | °C   |

| T <sub>STG</sub>                    | Storage temperature range                             | -65 to 85        | °C   |

| R <sub>(Load)</sub>                 | Minimum load resistance                               | 8                | Ω    |

| Electrostatic discharge             | Human body model                                      | ±2               | kV   |

| Electrostatic discharge             | Machine model                                         | ±200             | V    |

(\*1): Stress beyond those listed at "absolute maximum rating" table may cause permanent damage to the device. These are stress rating ONLY. For functional operation are strongly recommend follow up "recommended operation conditions" table. (\*2): BA3101 package embedded with an exposed thermal PAD underside of package. The exposed PAD performs the function of heat sink and it have to be connected to a thermally dissipating plane for power dissipation. Failure to do so will result in the device going into thermal protection shutdown.

#### PACKAGE DISSPATION RATINGS

| PACKAGE                     | $\theta_{ja}(junction to ambient air)$ | θjc(junction to case) | UNIT  |

|-----------------------------|----------------------------------------|-----------------------|-------|

| TQFP 48 pin with Expose Pad | 35.24                                  | 7.14                  | mW/°C |

\*This data was taken using 1 oz copper pad that is soldered directly to FR-4 PCB. The thermal pad must be soldered to the thermal land on PCB.

#### **RECOMMENDED OPERATING CONDITIONS**

Over operating free-air temperature range, unless otherwise specified

| SYMBOL PARAMETER |                | TEST CONDITION      | SPECIF |     |      |

|------------------|----------------|---------------------|--------|-----|------|

|                  |                | TEST CONDITION      | MIN    | MAX | UNIT |

| V <sub>DD</sub>  | Supply voltage | VDD , PVDDL , PVDDR | 8      | 15  | v    |

| SYMBOL           | PARAMETER                  | TEST CONDITION                                           | SPECIF         | UNIT                  |      |  |

|------------------|----------------------------|----------------------------------------------------------|----------------|-----------------------|------|--|

| STMBOL           | PANAMETEN                  | TEST CONDITION                                           | MIN            | MAX                   | UNIT |  |

| V <sub>IH</sub>  | High level input           | SHUTDOWN , MSTR/ SLV , SYNC , GAIN0 ,                    | 2.0            | 20                    |      |  |

|                  | voltage                    | GAIN1 <sup>,</sup> MUTE                                  |                |                       |      |  |

| V <sub>IL</sub>  | Low level input<br>voltage | SHUTDOWN , MSTR/ SLV , SYNC MUTE ,                       |                | 0.8                   | V    |  |

|                  |                            | GAIN0 , GAIN1                                            |                |                       |      |  |

|                  | High level input           | $V_I = V_{DD}$ , $V_{DD} = 15$ V                         |                | 150                   |      |  |

| I <sub>IH</sub>  | I <sub>IH</sub>            | MUTE , $V_I=V_{DD}$ , $V_{DD}=15 V$                      |                | 80                    | uA   |  |

|                  | current                    | V <sub>I</sub> =V <sub>REG</sub> , V <sub>DD</sub> =15 V |                | 2                     |      |  |

| IIL              | Low level input            | $V_{I}=V_{DD}$ , $V_{DD}=15$ V                           |                | 2                     |      |  |

|                  | current                    | V <sub>I</sub> =0 V · V <sub>DD</sub> =12 V              |                | 1                     | uA   |  |

| M                | High level output          |                                                          | V 0.0          |                       | V    |  |

| V <sub>OH</sub>  | voltage                    | FAULT,I <sub>OH</sub> =1 mA,                             | $V_{REG}$ -0.6 |                       | V    |  |

| V <sub>OL</sub>  | Low level output           | FAULT,I <sub>OL</sub> =-1 mA,                            |                | A .0.4                | V    |  |

| V <sub>OL</sub>  | voltage                    |                                                          |                | A <sub>GND</sub> +0.4 | v    |  |

| f <sub>OSC</sub> | Oscillator frequency       | $R_{OSC}$ Resistor = 100 k $\Omega$ · MSTR/ SLV = 2 V    | 250            | 300                   | kHZ  |  |

| T <sub>A</sub>   | Operating free-air         |                                                          | - 40           | 85                    | °C   |  |

| I A              | temperature                |                                                          | - 40           | 65                    | U    |  |

## **DC CHARACTERISTICS**

TA = 25°C, VDD= 12V, RL =  $8\Omega$ , Gain = 20dB (unless otherwise noted)

| SYMBOL              | PARAMETER                            | TEST CONDITION                            |           | SPECIFICATION |      |     | UNIT |

|---------------------|--------------------------------------|-------------------------------------------|-----------|---------------|------|-----|------|

| STMBOL              | FANAMETEN                            |                                           |           | MIN           | TYP  | MAX |      |

| V <sub>REG</sub>    | 5V internal supply voltage           | No load                                   |           |               | 5    | 5.5 | v    |

| V <sub>BYP</sub>    | Bypass reference for input amplifier | No                                        | 1.15      | 1.25          | 1.35 | v   |      |

| PSRR                | DC power supply rejection ratio      | V <sub>DD</sub> =12V, input AC            |           | 70            |      | dB  |      |

|                     | Drain-Source                         | V <sub>DD</sub> =12V, P <sub>O</sub> =8W, | High Side |               | 365  |     |      |

| R <sub>DS(ON)</sub> | on –state<br>resistance              | R <sub>L</sub> =8Ω                        | Low Side  |               | 365  |     | mΩ   |

|                     |                                      | GAIN0=L                                   | GAIN1=L   |               | 20   |     |      |

| G                   | Gain                                 | GAIN0=L                                   | GAIN1=H   |               | 26   |     | dB   |

| G                   | Gain                                 | GAIN0=H                                   | GAIN1=L   |               | 32   |     | ub   |

|                     |                                      |                                           | GAIN1=H   |               | 36   |     |      |

| SYMBOL PARAMETER          |               | TEST CONDITION                                      | SPE | UNIT  |     |      |

|---------------------------|---------------|-----------------------------------------------------|-----|-------|-----|------|

|                           |               | TEST CONDITION                                      | MIN | TYP   | MAX | UNIT |

| T <sub>ON</sub>           | Turn-On time  | C(V <sub>BYP</sub> )=1µF, SHUTDOWN =H               |     | 25    |     | ms   |

| T <sub>OFF</sub>          | Turn-Off time | C(V <sub>BYP</sub> )=1µF, SHUTDOWN =L               |     | 0.1   |     | ms   |

|                           | Quiescent     | SHUTDOWN =H, MUTE=L, no load, no filter, no snubber |     | 24    |     |      |

| I <sub>CC</sub> Mute mode |               | SHUTDOWN =H, MUTE=H, no load, no filter, no snubber |     | 11    |     | mA   |

|                           | Shutdown mode | SHUTDOWN =L, no load, no filter, no snubber         |     | 200µA |     |      |

## AC CHARACTERISTICS

TA = 25°C, VDD= 12V, RL = 8 $\Omega$ , Gain =20dB (unless otherwise noted)

| SYMBOL         | PARAMETER             | TEST CONDITION               |                                                                                     | SPE | CIFICA | TION | UNIT |  |

|----------------|-----------------------|------------------------------|-------------------------------------------------------------------------------------|-----|--------|------|------|--|

| STWDUL         | PANAMETEN             | 1251                         | TEST CONDITION                                                                      |     | TYP    | MAX  | UNIT |  |

| Ksvr           | Supply ripple         | 200mV <sub>PP</sub> ripple f | rom 20Hz-1kHz, input AC                                                             |     | 70     |      | dB   |  |

| 1\5V           | rejection             | i                            | tie ground                                                                          |     | 70     |      | uВ   |  |

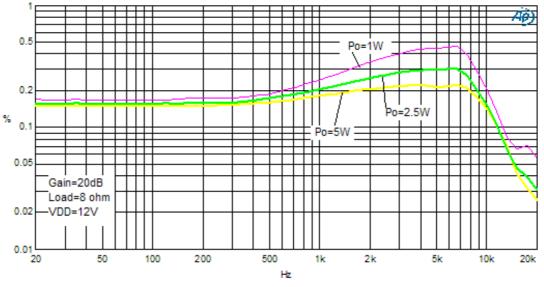

| THD+N          | Total harmonic        | f_1                          |                                                                                     |     |        |      | %    |  |

|                | distortion and noise  | f=1kHz, P <sub>0</sub> =5W   |                                                                                     |     | 0.17   |      | /0   |  |

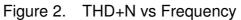

| Crosstalk      | Crosstalk between     | Vo-                          | Vo=1V <sub>BMS</sub> ,f=1kHz                                                        |     | 90     |      | dB   |  |

| Orossiaik      | L/R channel           | V0=                          |                                                                                     |     | 30     |      | üВ   |  |

|                |                       |                              | THD+N=1%                                                                            |     | 7.4    |      |      |  |

| Po             | Continuous output     | f=1kHz                       | THD+N=10%                                                                           |     | 9.2    |      | W    |  |

|                | power                 | bower                        | V <sub>DD</sub> =13V,THD+N=10%                                                      |     | 10.8   |      |      |  |

| SNR            | Signal to noise ratio | THD+N=1%                     |                                                                                     | 93  |        | dB   |      |  |

| V <sub>N</sub> | Output noise          | 22Hz to 22                   | <hz, a-weighted="" filter<="" td=""><td></td><td>150</td><td></td><td>μV</td></hz,> |     | 150    |      | μV   |  |

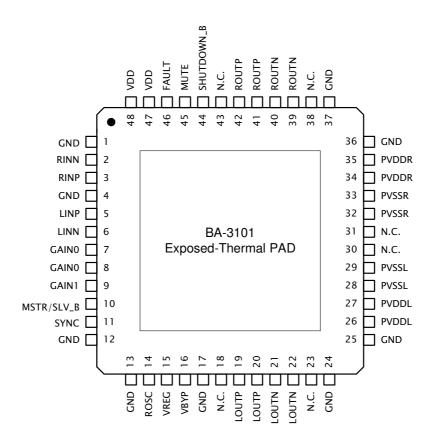

### **PIN ASSIGNMENTS**

## **PIN DESCRIPTION**

| Pin No. | Pin       | Туре         | I/O Pad Function                                                                                                                                                                                                    |

|---------|-----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND       | POWER        | Power ground                                                                                                                                                                                                        |

| 2       | RINN      | Input        | Right channel negative audio signal input                                                                                                                                                                           |

| 3       | RINP      | Input        | Right channel positive audio signal input                                                                                                                                                                           |

| 4       | GND       | POWER        | Power ground                                                                                                                                                                                                        |

| 5       | LINP      | Input        | Left channel positive audio signal input                                                                                                                                                                            |

| 6       | LINN      | Power        | Left channel negative audio signal input                                                                                                                                                                            |

| 7 ~ 8   | GAIN0     | Input        | Gain control input to select least significant bit                                                                                                                                                                  |

| 9       | GAIN1     | Input        | Gain control input to select most significant bit                                                                                                                                                                   |

| 10      | MSTR/ SLV | Input        | Determine clock operating mode. While this pin is H state, BA3101<br>operates in clock master mode, SYNC outputs operating clock, otherwise<br>the operating mode is clock Slave mode, SYNC pin accept clock input. |

| 11      | SYNC      | Input/Output | Could be input or output clock to synchronize multiple class D devices.<br>I/O direction is decided by "MSTR/ SLV " pin.                                                                                            |

| 12 ~ 13 | GND       | Power        | Power ground                                                                                                                                                                                                        |

| 14      | ROSC      | Input/Output | External resistor for current control                                                                                                                                                                               |

| 15      | VREG      | Output       | 5V voltage regulation output for internal reference.                                                                                                                                                                |

| 16      | VBYP      | Output       | Bias reference voltage output, need connect an external capacitor.                                                                                                                                                  |

| 17      | GND       | Power        | Power ground                                                                                                                                                                                                        |

| 18      | NC        |              |                                                                                                                                                                                                                     |

| 19 ~ 20 | LOUTP                  | Output | Left channel positive output                                                                                        |

|---------|------------------------|--------|---------------------------------------------------------------------------------------------------------------------|

| 21 ~ 22 | LOUTN                  | Output | Left channel negative output                                                                                        |

| 23      | NC                     |        |                                                                                                                     |

| 24 ~ 25 | GND                    | Power  | Power ground                                                                                                        |

| 26 ~ 27 | PVDDL                  | Power  | Power supply for left channel output                                                                                |

| 28 ~ 29 | PVSSL                  | Power  | Power ground for left channel output                                                                                |

| 30 ~ 31 | NC                     |        |                                                                                                                     |

| 32 ~ 33 | PVSSR                  | Power  | Power ground for right channel output                                                                               |

| 34 ~ 35 | PVDDR                  | Power  | Power supply for right channel output                                                                               |

| 36 ~ 37 | GND                    | Power  | Power ground                                                                                                        |

| 38      | NC                     |        |                                                                                                                     |

| 39 ~ 40 | ROUTN                  | Output | Right channel negative output                                                                                       |

| 41 ~ 42 | ROUTP                  | Output | Right channel negative output                                                                                       |

| 43      | NC                     |        |                                                                                                                     |

| 44      | SHUTDOWN_B             | Input  | Shutdown signal for IC (L state = disabled, H state= normal). TTL logic levels with compliance to V <sub>DD</sub> . |

| 45      | MUTE                   | Input  | Signal to instantly disable output; Signal is TTL logic level compatible and compliance with $V_{DD}$ .             |

| 46      | FAULT                  | Output | Fault status indicator. HIGH = short-circuit fault. LOW = fault-free. Only reports short-circuit faults.            |

| 47 ~ 48 | VDD                    | Power  | Power supply.                                                                                                       |

|         | Exposed Thermal<br>PAD |        | The thermal pad have to be soldered and be connect to the PCB large ground copper area.                             |

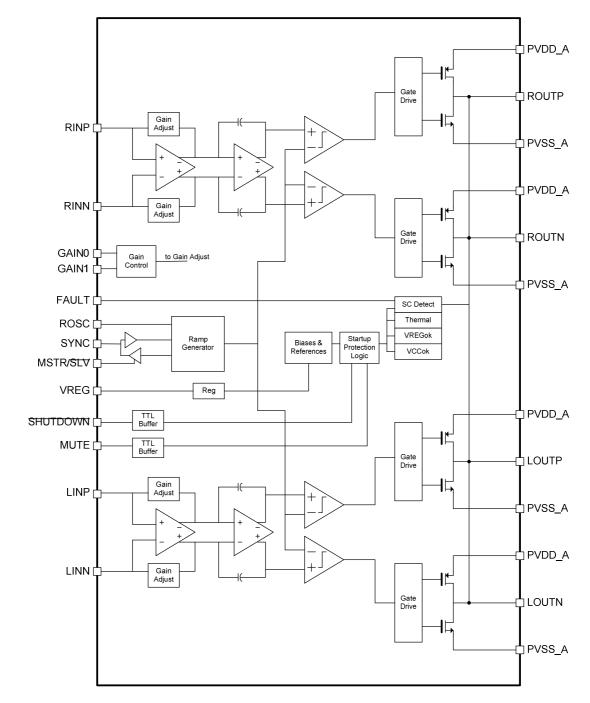

## FUNCTIONAL BLOCK DIAGRAM

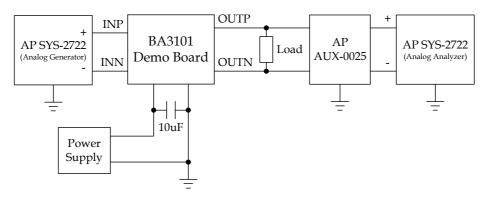

## **TEST SETUP FOR PERFORMANCE MEASUREMENTS**

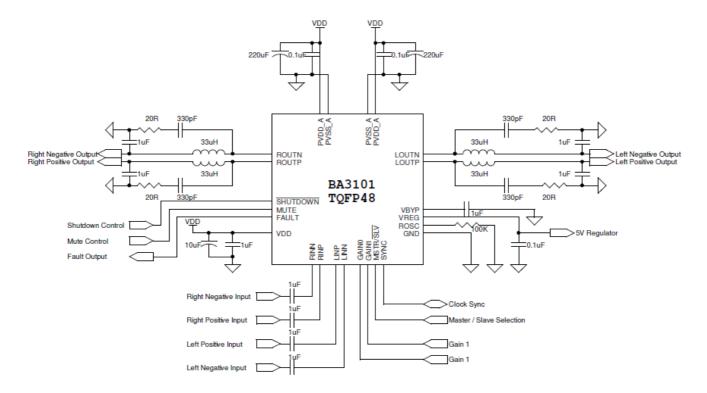

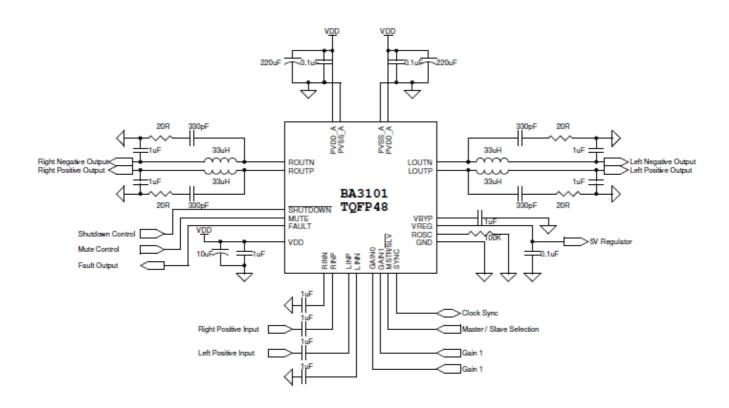

Note: This connection diagram shows single channel configuration. All graphs were measured by BA3101 demo board. Two 22µH inductors are used in series with load resistor to emulate the speaker for efficiency measurement.

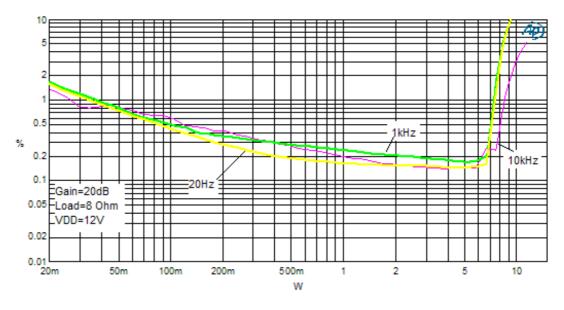

## TYPICAL CHARACTERISTICS

## **Table of Graphs**

| Figure No. | Description                     |                                                                                             |  |  |  |  |  |

|------------|---------------------------------|---------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1          | THD+N vs. Output Power          | Gain=20dB,Load=8Ω,VDD=12V                                                                   |  |  |  |  |  |

| 2          | THD+N vs. Output Frequency      | Gain=20dB,Load=8Ω,VDD=12V                                                                   |  |  |  |  |  |

| 3          | Crosstalk vs. Frequency         | Gain=20dB,Load=8Ω,VDD=12V,<br>THD+N=1%                                                      |  |  |  |  |  |

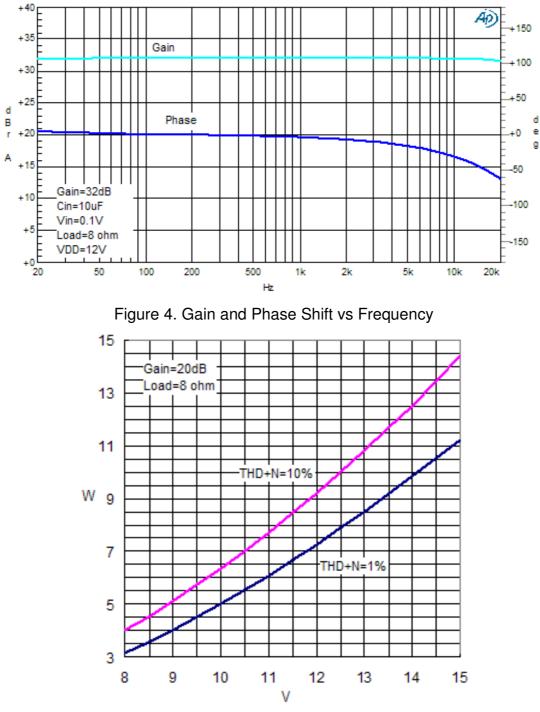

| 4          | Gain and Phase                  | $\begin{array}{l} Gain=32dB,Load=8\Omega,VDD=12V,\\ C_{IN}=10\mu F,V_{IN}=0.1V \end{array}$ |  |  |  |  |  |

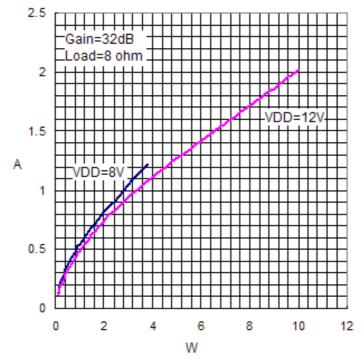

| 5          | Output Power vs. Supply Voltage | Gain=20dB,Load=8Ω                                                                           |  |  |  |  |  |

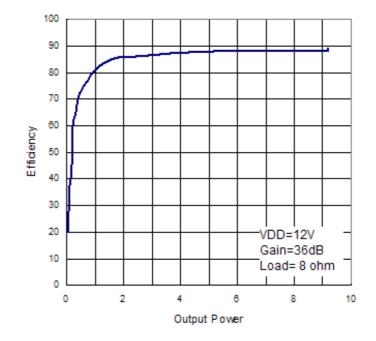

| 6          | Output Power vs. Current        | Gain=32dB,Load=8Ω                                                                           |  |  |  |  |  |

| 7          | Efficiency                      | Gain=32dB,Load=8Ω,VDD=12V                                                                   |  |  |  |  |  |

Important notice: Power above 10 W may require increased heatsinking.

Figure 1. THD+N vs Output Power

Figure 5. Output Power vs Supply

BA3101

Figure 6. Supply Current vs Output Power

## **FUNCTION DESCRIPTION**

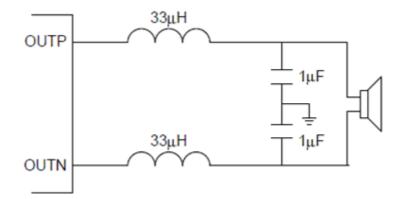

#### **Output Filter Application Note**

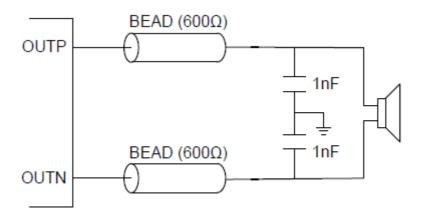

Design the BA3101 without the filter if the traces from amplifier to speaker are short (< 10cm), where the speaker is in the same enclosure as the amplifier is a typical application for class D without a filter. Many applications require a ferrite bead filter. The ferrite filter reduces EMI around 30MHz. When selecting a ferrite bead, choose one with high impedance at high frequencies, but low impedance at low frequencies.

Use an LC output filter if there are low frequency (<1 MHz) EMI sensitive circuits and there are long wires from the amplifier to the speaker.

Figure 9. Typical Ferrite Chip Bead Output Filter, Speaker Impedance=80

Inductors used in LC filters must be selected carefully. A significant change in inductance at the peak output current of the BA3101 will cause increased distortion. The change of inductance at currents up to the peak output current must be less than 0.1µH per amp to avoid this. Also note that smaller inductors than 33µH may cause an increase in distortion above what is shown in preceding graphs of THD versus frequency and output power. In all cases, avoid using inductors which value are less than 22µH.

Capacitors used in LC filters must also be selected carefully. A significant change in capacitance at the peak output voltage of the BA3101 will cause increased distortion. LC filter capacitors should have DC voltage ratings of at least twice the peak application voltage (the power supply voltage). In all cases, it is strongly recommended using capacitors with good temperature ratings like X5R.

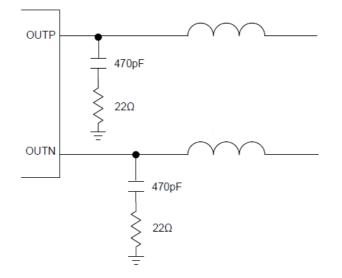

#### **Output Snubbers**

In Figure 11, the 470pF capacitors in series with  $22\Omega$  resistors from the outputs of the BA3101 to switching snubbers. They smooth switching transitions and reduce overshoot and ringing. By doing so they improve THD+N at lower power levels and they improve EMC by 2 to 4 dB at middle frequencies.

They increase quiescent current by 3mA to 11mA depending on power supply voltage.

Figure 10. Output Snubbers

#### **Over-Heat Protection**

Over-Heat protection on the BA3101 prevents damage to the device when the internal die junction temperature exceeds 150 ℃. Once the die temperature exceeds the thermal set point, the device enters the shutdown state and the outputs are disabled. The device will back to normal operation when die temperature is reduced without external system interaction.

#### **Output Short Protection**

The BA3101 has output short circuit protection circuitry on the outputs that prevents damage to the device during output-to-output short, output-to-GND short and output-to-VDD short. BA3101 enter the shutdown state and the outputs are disabled when detects output short. This is a latched fault and must be

reset by cycling the voltage on SHUTDOWN pin or MUTE pin, or by cycling the power off and then back

on. This clears the short circuit flag and allows for normal operation if the short was removed. If the short was not removed, the protection circuitry would active again.

#### **Internal 5V reference**

The VREG terminal (pin 15) is the output of an internally generated 5V supply, used for the oscillator, preamplifier, and gain control circuitry. It is highly recommended to place a 10nF~100nF capacitor close to the pin to keep the internal regulator stable. This regulated voltage should be used to connect GAIN0,

GAIN1, MSTR/ SLV , and MUTE terminals only. Do not use it to drive external circuitry.

#### **Bypass Capacitor**

The internal bias generator ( $V_{BYP}$ ) nominally provides a 1.25V bias for the preamplifier stages using internally. The input coupling capacitors and this internal voltage reference allow the inputs to be biased

within the optimal common-mode range of the input preamplifiers. The value of the capacitor on the  $V_{BYP}$  terminal (pin 16) is critical related to amplifier performance. During power up or recovery from the shutdown state, this capacitor determines the rate at which the amplifier starts up. Using a larger value of  $V_{BYP}$  capacitor can increase amplifier start-up time but should not exceed  $10\mu F$ .

#### Selection of Rosc

The class D output switching frequency can be controlled by Rosc and Cosc by the following equation:

$$f_{OUT} = \frac{1}{2 \times R_{OSC} \times C_{OSC}}$$

j

$R_{OSC}$  is an external resistance connected to pin 14 that is nominally  $100k\Omega$ .  $C_{OSC}$  is an internal capacitor that is nominally equal to 18 pF. Variation over fabrication process and temperature can result in a ±15% change in this capacitor value. For example, if  $R_{OSC}$  is fixed at  $100k\Omega$ , the frequency from device to device with this fixed resistance could vary from 300 kHz to 250 kHz including the variations of  $R_{OSC}$  resistor.

#### **LOW-ESR Capacitors**

Low-ESR capacitors are high recommended for this application. Generally a practical capacitor can be modeled simply as a resistor in series with an ideal capacitor. The voltage drop across this unwanted resistor can eliminate the effects of the ideal capacitor. Place low ESR capacitors on supply circuitry can improve THD+N performance.

#### **Decoupling Capacitors**

BA3101 requires appropriate power decoupling to minimize the output total harmonic distortion (THD). Power supply decoupling also prevents intrinsic oscillations for long lead lengths between the amplifier and the speaker. The optimum decoupling is achieved by using two capacitors of different types that target different types of noise on the power supply lines. For higher frequency spikes, or digital hash on the rail, a good low ESR ceramic capacitor, for example  $0.1\mu$ F to  $10\mu$ F, placed as close as possible to PVDD\_A pins works best. For filtering lower frequency noise, a larger low ESR aluminum electrolytic capacitor of 220µF or greater placed near the audio power amplifier is also recommended. The 220µF capacitor also serves as local storage capacitor for supplying current during heavy duty on the amplifier outputs. The PVDD\_A terminals provide the power to the output transistors, so a 220µF or larger capacitor should be placed on each channel PVDD\_A terminal. A 10µF ceramic capacitor on each VDD terminal is also recommended.

## **Gain Settings**

The gain of the BA3101 can be set by GAIN0 and GAIN1 pins. The gain ratios listed in Table are implemented by changing the taps on the feedback resistors in the preamplifier stage. Since the gain settings are controlled by ratios of input resistor and feedback resistor of the preamplifier, the gain ratio may varies with different  $V_{DD}$  supply. Note the amplifier gain ratio is obtained at 12V  $V_{DD}$  supply.

| Gain 1 | Gain 0 | Gain Ratio |

|--------|--------|------------|

| 1      | 1      | 36dB       |

| 1      | 0      | 32dB       |

| 0      | 1      | 26dB       |

| 0      | 0      | 20dB       |

Table 1. BA3101 Gain Ratio

#### **Differential Input**

The differential input stage of the amplifier can cancel any common-mode noise coupled from input paths. To use the BA3101 with a differential signal source, connect the positive output of the audio source to the INP input and the negative output from the audio source to the INN input. To use the BA3101 with a single-ended signal source, ac ground the INP or INN input through a coupling capacitor equal in value to the input capacitor on INN or INP and apply the audio source to either input. In single-ended input configuration, the unused inputs should be ac grounded at the audio source instead of at the IC input for better noise performance.

#### SHUTDOWN OPERATION

The BA3101 employs a shutdown mode of operation designed to reduce supply current to the absolute minimum level during periods of nonuse for power conservation. This terminal should be held high during normal operation when the amplifier is in normal operating. Pulling low causes the output drivers shutdown and the amplifier to enter a low-current state. Do not leave it unconnected, because there is no weakly pulling resistor inside the amplifier. Remember that to place the amplifier in the shutdown state prior to removing the power supply voltage so that power-off pop noise can be eliminated.

#### MSTR/ SLV and SYNC Operation

The MSTR/ SLV and SYNC terminals can be used to synchronize the frequency of the class D

output switching. When the MSTR/SLV terminal is high, the output switching frequency is determined by

the selection of the resistor connected to the ROSC terminal. The SYNC terminal becomes an output in this mode, and the frequency of this output is also determined by the selection of the ROSC resistor. This TTL compatible, push-pull output can be connected to another BA3101, configured in the slave mode. The output switching is synchronized to avoid any beat frequencies that could occur in the audio band when two class D amplifiers in the same system produces switching noises on V<sub>DD</sub> supply. When

MSTR/ SLV terminal is in low state, the output switching frequency is determined by the incoming square

wave on the SYNC input. The SYNC terminal becomes an input in this mode and accepts a TTL compatible square wave from another BA3101 configured in the master mode or from an external GPIO. If connecting to an external GPIO, recommended frequencies are 225 kHz to 325 kHz for proper device

operation.

## SAMPLE APPLICATION CIRCUIT

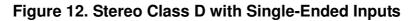

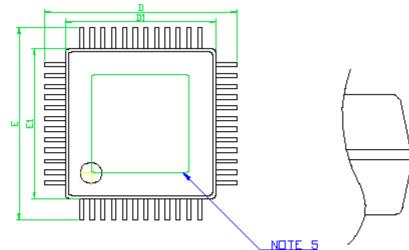

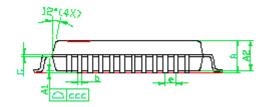

## **PACKAGE DIMENSION**

TQFP-48-EP

| SYMBOLS        | DIMENS | IONS IN MILLIM | TTER | DIMENSIONS IN INCH |            |        |

|----------------|--------|----------------|------|--------------------|------------|--------|

| STNDALS        | MIN    | NOM            | MAX  | MIN                | NOM        | MAX    |

| A              |        |                | 1.15 | —                  |            | 0.046  |

| A1             | 0.05   |                | 0.15 | 0.002              |            | 0.006  |

| A2             | 0.95   | 1.00           | 1.05 | 0.037              | 0.039      | 0.041  |

| b              | 0.17   | 0.22           | 0.27 | 0.006              | 0.008      | 0.011  |

| С              | 0.09   |                | 0.20 | 0.003              |            | 0.008  |

| D1             | 6.90   | 7.00           | 7.10 | 0.271              | 0.275      | 0.279  |

| D              | 8.80   | 9.00           | 9.20 | 0.346              | 0.354      | 0.362  |

| El             | 6.90   | 7.00           | 7.10 | 0.271              | 0.275      | 0.279  |

| Е              | 8.80   | 9.00           | 9.20 | 0.346              | 0.354      | 0.362  |

| e              | —      | 0.50(TYP)      |      |                    | 0.02(TYP)  | _      |

| L              | 0.45   | 0.60           | 0.75 | 0.018              | 0.024      | 0.029  |

| Ll             |        | 1.00(REF)      | _    |                    | 0.039(REF) | _      |

| <del>0</del> 1 | 0°     | 3.5°           | 7°   | 0°                 | 3.5°       | 7°     |

| CCC            |        |                |      |                    |            | 0.0035 |

- NOTE 1. PACKAGE BODY SIZES EXCLUDE MOLD FLASH AND GATE BURRS 2. DIMENSION L IS MEASURED IN GAUGE PLANE

- 3. TOLERANCE 0.10 mm UNLESS OTHERWISE SPECIFIED

- CONTROLLING DIMENSION IS MILLIMETER. CONVERTED INCH DIMENSIONS ARE NOT NECESSARILY EXACT.

DIE PAD EXPOSURE SIZE IS ACCORDING TO LEAD FRAME DESIGN.

- 6. FOLLOWED FORM JEDEC MO-136

TEL:0755-82863877 13242913995

panxia168@126.com